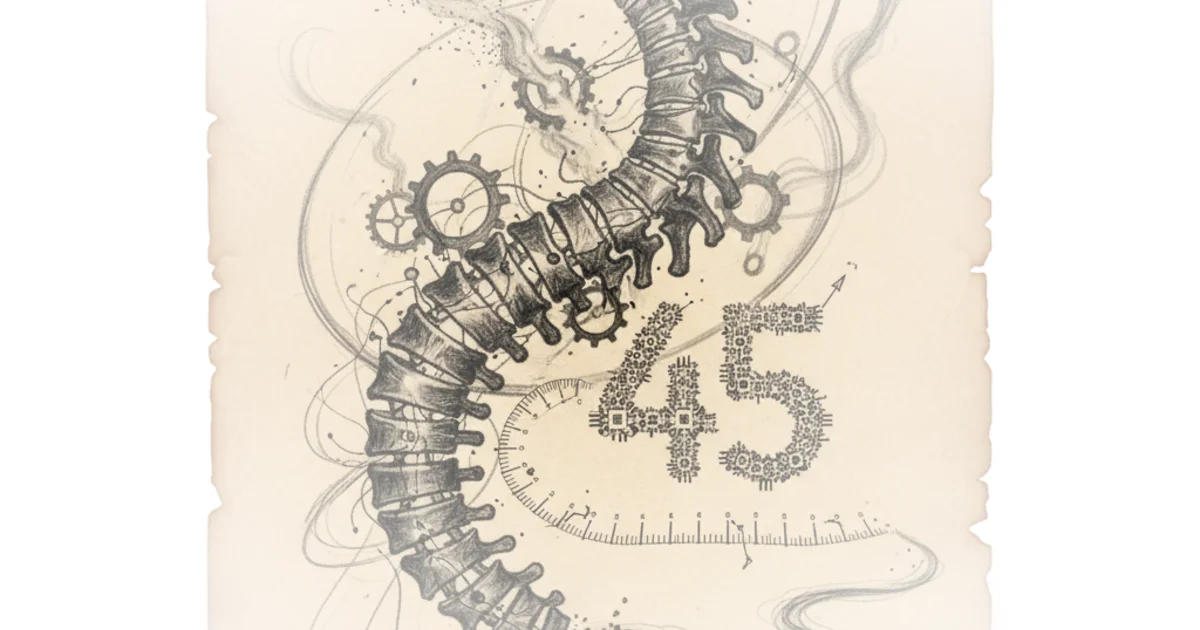

In an era obsessed with the cutting edge of 3nm and 2nm chips, Asianometry makes a compelling case for looking backward to understand the present. The piece argues that the 45nm process node, introduced in 2007, was not merely a stepping stone but a pivotal moment where the industry solved fundamental physics problems that still define modern manufacturing. This is not a nostalgic trip; it is a forensic examination of the engineering breakthroughs that made today's density possible.

The Invisible Foundations

Asianometry begins by dismantling the assumption that older nodes were simple. The author writes, "The process node's ultimate goal is to fabricate these very small devices at high volume. The devices must be consistently sized and perform reliably over a long period of time." This framing is crucial because it shifts the focus from raw speed to the brutal reality of yield and consistency. The commentary correctly identifies that without solving the microscopic chaos of impurities and crystal defects, scaling is impossible.

The piece details the rigorous inspection of silicon wafers, noting that "if these impurities get incorporated into the transistor, especially metal impurities, then it will cause the transistor's threshold voltage to fluctuate." This highlights a critical vulnerability in the supply chain: the purity of the raw material dictates the ceiling of the final product. Asianometry emphasizes that even the crystal structure must be perfect, stating, "Any interruptions, stacking faults or impurities in the crystal lattice can trap or interfere with the charge carriers moving through the silicon." This is a powerful reminder that at the atomic level, there is no room for error.

Critics might argue that focusing on 2007 technology is irrelevant for investors eyeing future growth, but this overlooks the fact that the fundamental physics of silicon cleaning and isolation have not changed. The methods developed then are the bedrock of current fabs.

The Evolution of Isolation

The most distinctive section of the coverage is the deep dive into how transistors are electrically isolated from one another. Asianometry writes, "Good fences make good neighbors, as goes the poet Robert Frost," using this metaphor to explain the necessity of preventing current leakage between billions of transistors. The author traces the industry's painful evolution from Local Oxidation of Silicon (LOCOS) to Shallow Trench Isolation (STI).

The failure of the older method is described vividly: "The shape of this encroachment looks like a bird's beak. So, they creatively named it bird's beaking." This phenomenon caused uneven surfaces that ruined the precision of later lithography steps. The transition to STI is presented as a masterclass in engineering problem-solving, where "STI digs shallow nanoscale trenches between transistors and fills them with insulation silicon dioxide in this case." The analogy of digging moats around castles effectively conveys the scale and purpose of the process.

The very act of cleaning making things dirtier. Sounds like me around the house.

Asianometry's inclusion of the historical context regarding cleaning methods adds a human element to the technical narrative. The author notes that early cleaning attempts using scrubbing brushes and harsh chemicals were ironic failures: "The very act of cleaning making things dirtier." This leads to the adoption of the RCA clean method, which remains the gold standard. The commentary on the RCA clean process is particularly strong, detailing the specific chemical baths used to strip organic films and metal contaminants without damaging the silicon lattice.

The Physics of Filling the Void

The final major argument concerns the challenge of filling the trenches created by STI. Asianometry explains that thermal oxidation, while useful for growing thin layers, fails to fill deep, narrow trenches uniformly. "The reason is because we want the silicon dioxide to get down to the very bottom of the trench and fill it completely and uniformly," the author writes. This necessitated the adoption of Tetraethyl Orthosilicate (TEOS) Chemical Vapor Deposition (CVD).

The piece describes the process of heating the wafer to high temperatures to decompose the TEOS vapor, forming a dense film. "Voids, seams, and low densities in the trench layers can lead to leakage and yield issues," Asianometry warns. This section underscores the immense difficulty of maintaining structural integrity at the nanoscale. The subsequent Chemical Mechanical Polishing (CMP) step is described as a delicate balancing act, where a laser senses the exposure of a silicon nitride stopping layer to prevent over-grinding.

A counterargument worth considering is that while the 45nm node solved the isolation problem, the industry has since faced new challenges with quantum tunneling and heat dissipation that STI alone cannot address. However, the foundational logic of the STI process remains unchanged.

Bottom Line

Asianometry's analysis succeeds in demystifying the complex, multi-step journey required to turn a raw silicon wafer into a functional chip. The strongest part of the argument is the demonstration that manufacturing is not just about shrinking transistors, but about mastering the chemistry and physics of the materials surrounding them. The piece's biggest vulnerability is its brevity; a deeper look at the economic trade-offs of these specific process choices would have added further weight. Readers should watch for how these foundational isolation techniques are being adapted for the extreme ultraviolet (EUV) lithography era, where the stakes for precision are even higher.